#### Fast Arithmetic

Philipp Koehn presented by Chang Hwan Choi

> 14 March 2018 27 Sept 2019

HW3-due foright

Midfern-Fr: 10/4

K Review on Wed 10/2

K Midfern 2016

Soon: 6502 review

questions

# arithmetic

## Addition (Immediate)

• Load immediately one number (s0 = 2)

li \$s0, 2

• Add 4 (\$s1 = \$s0 + 4 = 6)

addi \$s1, \$s0, 4

• Subtract 3 (\$s2 = \$s1 - 3 = 3)

addi \$s2, \$s1, -3

## Addition (Register)

• Load immediately one number (s0 = 2)

li \$s0, 2

• Add value from \$s5 (\$s1 = \$s0 + \$s5)

add \$s1, \$s0, \$s5

• Subtract value from \$s6 (\$s2 = \$s1 - \$s6)

sub \$s2, \$s1, \$s6

#### **Overflow**

- Signed integers operations: add, addi, and sub

- overflow triggers exceptions

- similar to interrupt

- register \$mfc0 contains address of exception program

- Unsigned integers operations: addu, addiu, and subu

- no overflow handling (as in C programming language)

## Code for Detecting Overflow

Security!

- Overflow for unsigned integers operations can be detected from result

- Actual detection code is a bit intricate

- If you are interested

- → consult Section 3.2 in Patterson/Hennessy textbook

unsigned a,b,sum;

scanf ("20u 20u",

&a, &b);

Sum = a + b;

if (sum < a) {

// overflow

:

## fast addition

11

+11

\_\_\_\_

\_\_\_\_

1+1 = 0, carry the 1

```

11

+11

---

11

---

10

```

1+1+1 = 1, carry the 1

11

+11

\_\_\_

11

\_\_\_

110

copy carry bit

#### Fast Addition

• We defined n-bit adding as a sequential process

propagation delay: time between input of gate Changing fo output changing

ullet More bits o addition takes longer

• 32 bit addition gets very slow

critical path:

longest/slovest path

through a (sub)circuit

from input to output

Carry Lookahead • Faster addition:

## Problem: Carry Propagation

• 1+1 addition always causes a carry

• 0+0 addition never causes a carry

$$0+0 + carry1 = 1$$

, carry  $0$

$0+0 + carry0 = 0$ , carry  $0$

• 0+1 and 1+0 addition may cause a carry

$$0+1 + carry1 = 0$$

, carry 1  $0+1 + carry0 = 1$ , carry 0

## Generate and Propagate

• Compute for each bit, if it generates or propagates carry

• Example

| Operand A | 0100 1111 |

|-----------|-----------|

| Operand B | 0110 0001 |

| Generate  | 0100 0001 |

| Propagate | 0110 1111 |

| Carry     | 1001 111- |

generate -> propagate

• Generate: a<sub>i</sub> AND b<sub>i</sub>

• Propagate: a<sub>i</sub> OR b<sub>i</sub>

• Carry: ?

• First compute generate and propagate for all bits

- generate:  $g_i = a_i \text{ AND } b_i$

- propagate:  $p_i = a_i \text{ OR } b_i$

- First compute generate and propagate for all bits

- generate:  $g_i = a_i \text{ AND } b_i$

- propagate:  $p_i = a_i \text{ OR } b_i$

- Compute carries for each bit

- $c_1 = g_0 \text{ OR } (p_0 \text{ AND } c_0)$

- First compute generate and propagate for all bits

- generate:  $g_i = a_i \text{ AND } b_i$

- propagate:  $p_i = a_i \text{ OR } b_i$

- Compute carries for each bit

- $c_1 = g_0 \text{ OR } (p_0 \text{ AND } c_0)$

- $-c_2=g_1 ext{ OR } (p_1 ext{ AND } g_0) ext{ OR } (p_1 ext{ AND } p_0 ext{ AND } c_0)$

• First compute generate and propagate for all bits

- generate:

$$g_i = a_i AND b_i$$

- propagate:

$$p_i = a_i \text{ OR } b_i$$

- The carry computations require no recursion

- --- but use a lot of gates Moore's law

- We may want to stop at 4 bits with this idea

- Combine 4 4-bit adders

- For each 4-bit adder, compute

- "super" propagate =  $P = p_0$  AND  $p_1$  AND  $p_2$  AND  $p_3$

- Combine 4 4-bit adders

- For each 4-bit adder, compute

- "super" propagate =  $P = p_0$  AND  $p_1$  AND  $p_2$  AND  $p_3$

- "super" generate =  $g_3$  OR  $(p_3$  AND  $g_2)$  OR  $(p_3$  AND  $p_2$  AND  $g_1)$  OR  $(p_3$  AND  $p_2$  AND  $p_1$  AND  $g_0)$

- Combine 4 4-bit adders

- For each 4-bit adder, compute

- "super" propagate =  $P = p_0$  AND  $p_1$  AND  $p_2$  AND  $p_3$

- "super" generate =  $g_3$  OR  $(p_3$  AND  $g_2)$  OR  $(p_3$  AND  $p_2$  AND  $g_1)$  OR  $(p_3$  AND  $p_2$  AND  $p_1$  AND  $g_0)$

- $\bullet$  Compute super carry  $\textbf{C}_j$  from super propagate  $\textbf{P}_j$  and super generate  $\textbf{G}_j$

- Use C<sub>j</sub> as input carry to the 4-bit adders

## Cycles

- 1. compute propagate  $p_i$  and generate  $g_i$

- 2. compute carry  $c_{\rm i}$  compute super propagate  $P_{\rm j}$  and super generate  $G_{\rm j}$

- 3. compute super carry  $C_j$

- 4. carry out all bitwise additions

parallelism

#### Trade-Off

- ullet Higher n in n-bit adders

- more gates in circuit

- faster computation

- Modern CPUs can pack more gates on a chip

- $\Rightarrow$  speed-up at same clock speed

# multiplication

• Elementary school multiplication:

10101 x 1101

- Idea

- shift second operand to right (get last bit)

- if carry: add second operand to sum

- rotate first operand to left (multiply with binary 10)

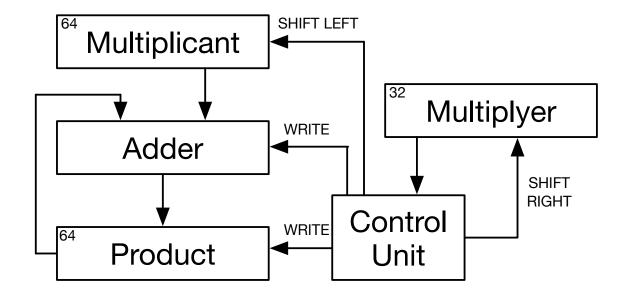

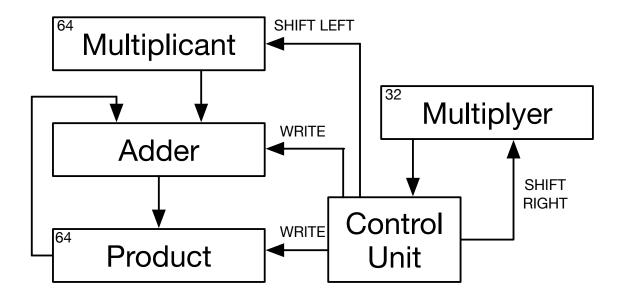

## Multiplication in Hardware

• Control unit runs microprogram

loop 32 times:

if lowest bit of multiplyer=1

add multiplicant to product

shift multiplicant left

shift multiplyer right

• Note: multiplying 32 bit numbers may result in 64 bit product

## Multiplication in Hardware

• Control unit runs microprogram

loop 32 times:

if lowest bit of multiplyer=1

add multiplicant to product

shift multiplicant left

shift multiplyer right

- Speed

- 32 iterations

- 3 operations each

(add + shift + shift)

- ightarrow almost 100 operations

• Note: multiplying 32 bit numbers may result in 64 bit product

## Parallelize the 3 Operations

• The 3 operations in each loop affect different registers

- add: product

- shift left: multiplicant

- shift right: multiplyer

$\Rightarrow$  These can be executed in parallel

(note: read is executed before write)

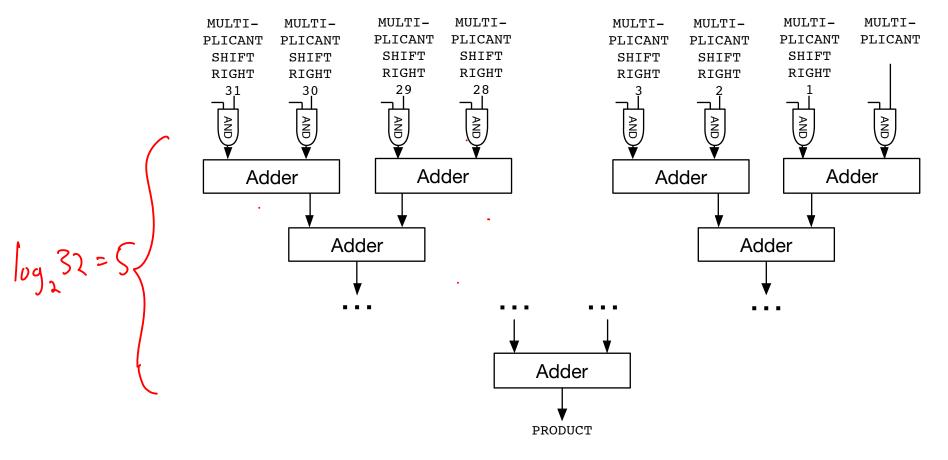

## Parallelize the Iterations

• Sum of 32 independently computed values

#### Parallelize the Iterations

- Sum of 32 independently computed values

- ullet More adders o some summing can be done in parallel

#### Parallelize the Iterations

- Sum of 32 independently computed values

- ullet More adders o some summing can be done in parallel

- Binary tree  $\rightarrow \log_2 32 = 5$  cycles

• 32 bit multiplication results in 64 bit product

• 32 bit multiplication results in 64 bit product

• Special 64 bit register holds result

- hi: high word

- lo: low word

• 32 bit multiplication results in 64 bit product

• Special 64 bit register holds result

- hi: high word

- lo: low word

• Low word has to be retrieved by another instruction

• 32 bit multiplication results in 64 bit product

• Special 64 bit register holds result

- hi: high word

- lo: low word

• Low word has to be retrieved by another instruction

• Since this is the typical usage, pseudo-instruction

More on that later

# division

1011 / 10 =

# Elementary School Division Aivident division 1011 / 10 =

| 1011  | / | 10 | = | 10 |

|-------|---|----|---|----|

| 10    |   |    |   |    |

| <br>0 |   |    |   |    |

| 01    |   |    |   |    |

| 011   |   |    |   |    |

| 1011 / 10 = 101 |  |  |  |  |

|-----------------|--|--|--|--|

| 10              |  |  |  |  |

| 0               |  |  |  |  |

| 01              |  |  |  |  |

| 011             |  |  |  |  |

| 10              |  |  |  |  |

| 1 Remainder     |  |  |  |  |

| 1011 | / 10 = 101 |

|------|------------|

| 10   |            |

| 0    |            |

| 01   |            |

| 011  |            |

| 10   |            |

| 1    | Remainder  |

#### • Algorithm

- 1. shift divisor sufficiently to the left

- 2. check if subtraction is possible yes  $\rightarrow$  add result bit 1, carry out subtraction no  $\rightarrow$  add result bit 0

- 3. pull down bit from dividend

- 4. shift divisor to the right not possible  $\rightarrow$  done, note remainder otherwise go to step 2

- 1. Shift divisor sufficiently to the left

- hard for machine to determine

- $\rightarrow$  shift to maximum left

- 32 bit division: use 64 register, push 32 positions

- 1. Shift divisor sufficiently to the left

- hard for machine to determine

- $\rightarrow$  shift to maximum left

- 32 bit division: use 64 register, push 32 positions

- 2. Check if subtraction is possible yes  $\to$  add result bit 1, carry out subtraction no  $\to$  add result bit 0

- we always carry out subtraction

- if overflow, do not use result

- 1. Shift divisor sufficiently to the left

- hard for machine to determine

- $\rightarrow$  shift to maximum left

- 32 bit division: use 64 register, push 32 positions

- 2. Check if subtraction is possible yes  $\to$  add result bit 1, carry out subtraction no  $\to$  add result bit 0

- we always carry out subtraction

- if overflow, do not use result

- 3. Pull down bit from dividend

Condihona

- 1. Shift divisor sufficiently to the left

- hard for machine to determine

- $\rightarrow$  shift to maximum left

- 32 bit division: use 64 register, push 32 positions

- 2. Check if subtraction is possible yes  $\to$  add result bit 1, carry out subtraction no  $\to$  add result bit 0

- we always carry out subtraction

- if overflow, do not use result

- 3. Pull down bit from dividend

- 4. Shift divisor to the right not possible  $\rightarrow$  done, note remainder otherwise go to step 2

#### Division in Hardware

- Operations similar to multiplication

- shift divisor

- subtraction

- indication if subtraction should be accepted

- These operations can be parallelized

- But: iterations cannot be parallelized the same way

(sophisticated prediction methods guess outcome of subtractions)

• 32 bit division results in 32 bit quotient and 32 bit remainder

- hi: remainder

- lo: quotient

• 32 bit division results in 32 bit quotient and 32 bit remainder

- hi: remainder

- lo: quotient

• Quotient has to be retrieved by another instruction

• 32 bit division results in 32 bit quotient and 32 bit remainder

- hi: remainder

- lo: quotient

• Quotient has to be retrieved by another instruction

div \$s1, \$s2 mflo \$s0